#### МИНИСТЕРСТВО СЕЛЬСКОГО ХОЗЯЙСТВА РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение высшего образования «Российский государственный аграрный университет – MCXA имени К.А.Тимирязева»

Кафедра «Автоматизации и роботизации технологических процессов имени академика И.Ф. Бородина»

Ю.А. Судник, Е.А. Четвериков, Е.А. Шабаев, В.Н. Беленов

## «Электронные компоненты микропроцессорных устройств»

Лабораторный практикум

| Содержание                                                     | Стр. |

|----------------------------------------------------------------|------|

| 1. Тема 1 Исследование цифровых счетчиков импульсов            | 3    |

| 2. Тема 2 Исследование арифметико-логического                  |      |

| устройства (АЛУ)                                               | 17   |

| 3. Тема 3 Исследование оперативной памяти и мультиплексной     |      |

| организации шины данных                                        | 33   |

| 4. Тема 4 Исследование оперативного запоминающего устройства и |      |

| мультиплексного способа организации внутренней шины данных     | 33   |

Судник Ю.А., Четвериков Е.А., Шабаев Е.А., Беленов В.Н.

**«Электронные компоненты микропроцессорных устройств»:** Лабораторный практикум / Ю.А. Судник. М.: Изд-во РГАУ-МСХА, 2025. 40 с.

**Рецензент** Нормов Д.А., и.о. заведующего кафедрой электроснабжения и теплоэнергетики имени академика И.А. Будзко

В методических указаниях «Электронные компоненты микропроцессорных устройств»:» рассмотрены принципы функционирования и структурные особенности ключевых элементов цифровых вычислительных систем: счетчиков, арифметико-логических устройств (АЛУ), оперативной памяти (ОЗУ) и архитектуры микропроцессора. Представлены теоретические основы, методики проведения экспериментов и контрольные вопросы для закрепления материала.

Предназначено для бакалавров, обучающихся по направлению 35.03.06 – «Агроинженерия»

Рекомендовано к изданию учебно-методической комиссией энергетического факультета (протокол № от 2025 г.)

© Судник Ю.А. Четвериков Е.А., Шабаев Е.А., Беленов В.Н., 2025

©ФГБОУ ВПО РГАУ-МСХА им. К.А. Тимирязева, 2025

©Издательство РГАУ-МСХА, 2025

#### Тема 1 «Исследование цифровых счетчиков импульсов»

#### I. Цель работы.

Изучить принципы функционирования и исследование характеристик основных типов цифровых счетчиков (суммирующих, вычитающих, реверсивных) на базе триггерных элементов.

#### II. Задание.

- 1. Исследовать схему суммирующего счётчика с переменным модулем счёта  $K_C$ .

- 2. Исследовать схему вычитающего счётчика.

- 3. Исследовать схему реверсивного счётчика.

#### III. Теоретические сведения.

<u>Счётчик импульсов</u> — это последовательное цифровое устройство (ЦУ), обеспечивающее хранение слова информации и выполняющее над этим словом микрооперации счёта. Микрооперация счёта заключается в изменении значения числа 0 в счётчике на  $\pm 1$ . Счётчик, в котором выполняется микрооперация счёта C:=C+1, называется суммирующим, а счётчик, реализующий микрооперацию C:=C-1, — вычитающим. Счётчик называется реверсивным, если реализуются обе микрооперации.

Основным параметром счётчика является модуль (коэффициент) счёта  $K_C$ , определяемый максимальным числом единичных сигналов, которое может быть сосчитано счётчиком. Счётчик, содержащий п двоичных разрядов, может находиться в состояниях  $0, 1, 2, \ldots, 2^{\Pi}$  -1. При поступлении на вход суммирующего счётчика  $2^{\Pi}$  — ой единицы он переходит из состояния  $2^{\Pi}$  —1 в состояние 0. Таким образом, п — разрядный суммирующий двоичный счётчик имеет модуль счёта  $K_C = 2^{\Pi}$ .

Счётчики обычно реализуются на T-триггерах, однако могут использоваться и D-, JK-триггеры.

Классификация счётчиков. В зависимости от направления счёта различаются суммирующие (с прямым счётом), вычитающие (с обратным счётом) и реверсивные (с прямым и обратным счётом) счётчики. По организации схемы переноса различаются счётчики с последовательным, параллельным и параллельно-последовательным переносом.

В зависимости от наличия синхронизации различаются <u>синхронные</u> и <u>асинхронные</u> счётчики. При маркировке счётчика для обозначения его функциональной принадлежности (см. лабораторную работу №1) используются буквы ИЕ. Конструктивно счётчик выполняется в виде совокупности интегральных схем – триггеров, соединённых соответствующим образом, или в виде одной интегральной схемы, содержащей многоразрядный счётчик.

Ниже рассмотрим основные типы счётчиков.

#### Суммирующие счётчики.

Рассмотрим устройство 3—разрядного суммирующего двоичного асинхронного счётчика. В таком счётчике можно реализовать счётную последовательность от 0 до  $2^3$  –1 = 7. Последовательность чисел может быть задана совокупностью 3—разрядных двоичных чисел  $b_3$   $b_2$   $b_1$ : 000, 001, 010, 011, 100, 101, 110, 111.

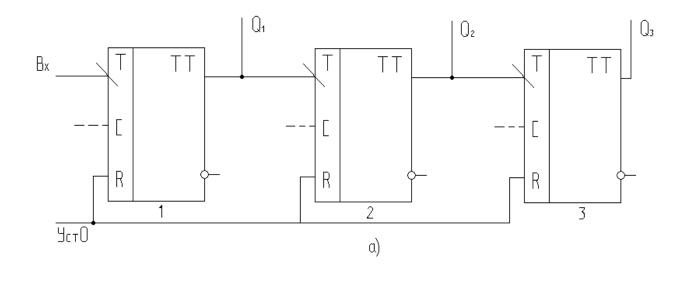

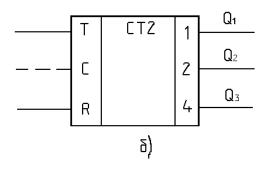

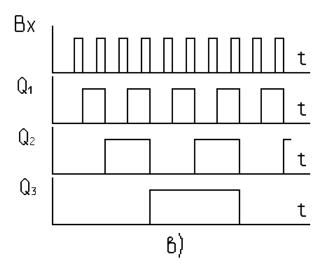

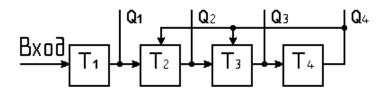

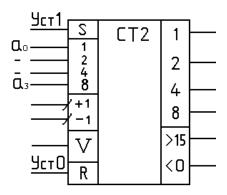

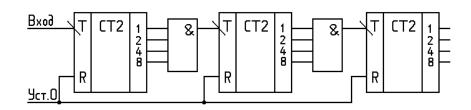

Поставим в соответствие каждому разряду  $b_i$  числа выход триггера  $Q_i$ . В 3-разрядном счётчике с выходами  $Q_3$   $Q_2$   $Q_1$  будет реализоваться счётная последовательность от 0 до 7. Схема такого счётчика приведена на рис. 1 а. В этой схеме исходное состояние счётчика устанавливается подачей сигнала оп шине «Уст. 0». Триггеры изменяют своё состояние с окончанием входного сигнала (переключение по срезу - см. лабораторную работу №3), т. е. после перехода от уровня 1 к 0. Работа такого триггера описывается временной диаграммой на рис. 1 в. На рис. 1 б изображён этот же счётчик, но в интегральном исполнении, где CT2 означает двоичный счётчик; выходы 1, 2, 4 означают веса двоичных разрядов ( $2^0 = 1$ ,  $2^1 = 2$ ,  $2^2 = 1$ ), соответствующих выходам  $Q_1$ ,  $Q_2$ ,  $Q_3$ ; T— счётный вход; R — установка нуля.

Рис. 1.1. Суммирующий двоичный асинхронный счётчик

Работа счётчика. После подачи сигнала «Уст. 0» счётчик находится в нулевом состоянии. Это соответствует наличию уровня 0 на выходах  $Q_1$ ,  $Q_2$ ,  $Q_3$ . Дальнейшее изменение состояния счётчика целиком будет зависеть только от входного сигнала (так работает асинхронный счётчик). С приходом первого

сигнала на вход первый триггер переходит в состояние 1 ( $Q_I = 1$ ;  $\overline{Q}_1 = 0$ ) и на его выходе устанавливается уровень 1. Триггеры 2 и 3 продолжают сохранять нулевое состояние, поскольку сигнал на их входах не изменяется с уровня 1 на уровень 0, т. е.  $Q_2 = 0$ ,  $Q_3 = 0$ . С приходом второго сигнала триггер 1 переходит из состояния 1 в состояние 0. В момент изменения уровня на его выходе с  $Q_I = 1$  на уровень  $Q_I = 0$  триггер 2 переходит в состояние 1 и на его выходе устанавливается уровень  $Q_2 = 1$ . Состояние триггера 3 остаётся неизменным. Этот триггер перейдёт в состояние 1 лишь при поступлении на счётный вход триггера 1 четвёртого по счёту сигнала. При этом триггер 1 перейдёт в состояние 0. Переход от состояния 0 к состоянию 0 вызовет изменение уровней от 1 к 0 на счётном входе триггера 2.

В результате триггер 2 также перейдёт из состояния 1 в состояние 0. Такой переход повлечёт за собой изменение уровня от 1 к 0 на счётном входе триггера 3. В результате на выходе  $Q_3$  установится уровень 1. При этом выходах  $Q_1$  и  $Q_2$  будут уровни 0. Следовательно, в счётчике будет зафиксировано числю 4 в двоичном представлении ( $4_{10} = 100_2$ ). Это соответствует фиксации момента поступления четвёртого сигнала. К моменту поступления восьмого по счёту сигнала на выходах триггеров  $Q_1$ ,  $Q_2$ ,  $Q_3$  будет установлен уровень 1. Поступление восьмого сигнала на счётный вход триггера 1 вызовет изменение его состояния с 1 на 0. В свою очередь, изменение состояния триггера 1 вызовет изменение состояния триггера 2, что в свою очередь приведёт к изменению состояния триггера 3. В результате все триггеры счётчика перейдут в состояние 0. Счётчик будет подготовлен к счёту новой последовательности из восьми сигналов.

Закон функционирования счётчика можно представить в виде таблицы состояний триггеров.

Состояние триггеров

| Nº                    | Положения триггеров   |                       |                       | Nº               | Положения триггеров   |                  |                       |

|-----------------------|-----------------------|-----------------------|-----------------------|------------------|-----------------------|------------------|-----------------------|

| сост.                 | Q <sub>1</sub>        | Q <sub>2</sub>        | <b>Q</b> <sub>3</sub> | сост.            | <b>Q</b> <sub>1</sub> | $Q_2$            | <b>Q</b> <sub>3</sub> |

| 0<br>1<br>2<br>3<br>4 | 0<br>0<br>0<br>0<br>1 | 0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>0 | 5<br>6<br>7<br>8 | 1<br>1<br>1<br>0      | 0<br>1<br>1<br>0 | 1<br>0<br>1<br>0      |

Работа рассмотренного счётчика происходит оп модулю  $K_C = 2^{\Pi}$ , где п—число триггеров. На практике возникает потребность в построении счётчиков по произвольному модулю  $K_C$  с числом двоичных разрядов, выбираемых исходя из условия:

$$2^{\Pi} \le K_C < 2^{\Pi+1}$$

Это вызывает необходимость исключения лишних состояний в счётчике, что делается с помощью разнообразных способов. Наибольшее распространение получили способ принудительной установки в состояние «0» всех разрядов двоичного счётчика и способ принудительного насчёта [2].

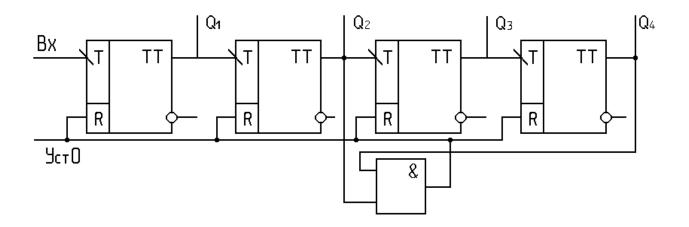

По первому способу реализуются счётчики с естественным порядком счёта, по второму - счётчики с принудительным насчётом. В счётчиках с <u>естественным порядком счёта</u> порядок счёта такой же, как в двоичных счётчиках. Отличие заключается в том, что путём введения дополнительных связей счёт заканчивается раньше значения  $2^{\Pi}$ . Так, у счётчика с  $K_C = 10$  переход разрядов в состояние «0» будет происходить с приходом не 16—го, а 10—го счётного импульса («система 16—6»). Пример построения счётчика с естественным порядком счёта при  $K_C = 10$  приведён на рис. 1.2.

Рис. 1.2. Счётчик с естественным порядком счёта при  $K_C = 10$

До наступления 10-го счётного импульса последовательность включения триггеров та же, что и у двоичного счётчика (табл. 2). С приходом 10го импульса срабатывает схема И, происходит сброс всех триггеров в «0» и счёт происходит сначала.

Таблица 1.2 Последовательность включения триггеров Положение триггеров

| Состояния  | TIONOMOTINO TENTIOPOS                                       |

|------------|-------------------------------------------------------------|

| RINHROTOGO | Q <sub>4</sub> Q <sub>3</sub> Q <sub>2</sub> Q <sub>1</sub> |

| 0          | 0 0 0 0                                                     |

| 1          | 0 0 0 1                                                     |

| 2          | 0 0 1 0                                                     |

| 3          | 0 0 1 1                                                     |

| 4          | 0 1 0 0                                                     |

| 5          | 0 1 0 1                                                     |

| 6          | 0 1 1 0                                                     |

| 7          | 0 1 1 1                                                     |

| 8          | 1 0 0 0                                                     |

| 9          | 1 0 0 1                                                     |

| 10         | 0 0 0 0                                                     |

В счётчиках с принудительным насчётом исключение избыточных состояний двоичного счётчика достигается путём принудительной установки отдельных его разрядов в состояние 1 в процессе счёта. Принудительный насчёт осуществляется введением обратных связей со старших разрядов счётчика в младшие, благодаря чему соответствующие младшие разряды вне очереди переключаются в состояние 1.

Вследствие принудительного насчёта показания рассматриваемых счётчиков не соответствуют двоичной системе счисления. По этой причине их относят к классу счётчиков с произвольным порядком счёта.

Способ реализации счётчиков с принудительным насчётом в процессе счёта покажем на примере структурной схемы счётчика с  $K_C = 10$  (рис. 3).

Рис. 1.3. Счётчик с принудительным насчётом

Схема состоит из четырёх триггеров и цепей обратных связей с выхода четвёртого разряда на запись «1» во второй и третий разряды. До записи «1» в четвёртый разряд, т. е. до прихода восьмого счётного импульса, счётчик работает как двоичный (табл. 3). С приходом восьмого счётного импульса «1» записывается в триггер  $T_4$  с осуществлением обратной связи на запись «1» во вторую и третью ячейки. Таким образом, после восьмого счётного импульса, вследствие принудительного насчёта, в счётчик записывается число 8+6=14. Девятый счётный импульс устанавливает «1» в триггер  $T_1$ , а 10-й счётный импульс возвращает счётчик в исходное нулевое состояние.

Счётчик с  $K_C = 10$  называется десятичным или декадным. Этот счётчик нашёл широкое применение для регистрации числа импульсов с последующим визуальным отображением результата. Десятичные счётчики часто включают последовательно (рис. 1.4).

Рис. 1.4. Последовательное включение десятичных счетчиков

Если в пределах всех декад счёт ведётся в двоичной системе счисления, то, например, числу  $987_{10}$  будет отвечать код  $1001\ 0111\ 1000_2$ , характеризующий двоично—десятичную систему счисления всего счётного устройства.

Все существующие типы счётчиков (в том числе и те, которые рассмотрены ниже) могут быть реализованы как асинхронные, так и синхронные. В последнем случае на входы C триггеров должны одновременно со счётным поступать синхроимпульсы (см. рис.  $1.1\,\mathrm{a}$ ).

#### Вычитающие и реверсивные двоичные счётчики

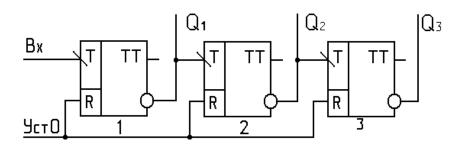

В вычитающих счётчиках с приходом очередного счётного сигнала предыдущий результат уменьшается на единицу, таким образом реализуется последовательность чисел, начиная с  $2^{\Pi}-1$  и кончая 0. После получения значения 0 последовательность повторяется. Вычитающий счётчик в отличие от суммирующего строится так, что со входом каждого последующего триггера соединяется инверсный выход предыдущего триггера (см. рис. 5).

Рис.1.5. Вычитающий счетчик

В реверсивном счётчике объединяются схемы суммирующего и вычитающего счётчиков. Кроме того, существует возможность управления направлением счёта с помощью дополнительного устройства. Схема реверсивного счётчика в интегральном исполнении приведена на рис. 1.6. Для счётных сигналов предусмотрены два входа. Если счётчик работает как суммирующий, сигналы счёта следует подавать на вход +1. Для вычитающего счётчика сигналы счёта подаются на вход –1. На выходе счётчика, обозначенном >15,

сигнал появляется при переходе счётчика в состояние с номером 15, в котором все триггеры установлены в 1. На этом выходе формируется сигнал переноса в следующий счётчик. На выходе <0 сигнал появляется при заполнении счётчика нулями. Это сигнал займа в следующий счётчик в схеме вычитающего счётчика. Допускается установка заданного исходного состояния счётчика с помощью ввода в счётчик нужной кодовой комбинации  $a_0$ ,  $a_1$ ,  $a_2$ ,  $a_3$  при наличии разрешения на входе V.

Рис. 1.6. Схема реверсивного счётчика в интегральном исполнении

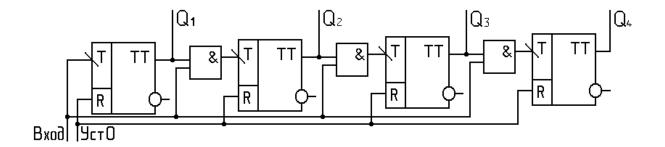

Рассмотренные схемы счётчиков на рис. 1.1 и рис. 1.2 называются счётчиками с последовательным переносом. В таких счётчиках есть существенный недостаток — накапливать от разряда к разряду время задержки  $t_3 = \pi t_{\Pi}$  (на рис. 1 в. это время не учтено), где  $t_{\Pi}$  — время переключения триггера. Время задержки растёт с ростом числа разрядов в счётчике. Поэтому это время ограничивает максимальную частоту подачи сигналов на вход, тем самым ограничивается быстродействие счётчика. Для уменьшения времени задержки распространения переносов используются счётчики с параллельным и параллельно-последовательным переносом.

#### Счётчики с параллельным и параллельно-последовательным переносом.

Пример выполнения двоичного счётчика с <u>параллельным переносом</u> представлен на рис. 7.

Рис.1.7. Двоичный счётчик с параллельным переносом

Задержка определяется только схемами И и значительно в меньшей степени количеством разрядов в счётчике. Схемы И используются для формирования «сквозных» переносов, при которых единица даже в самый старший разряд заносится почти одновременно с поступлением импульса счёта.

Работа счётчика с таким переносом основана на следующей закономерности двоичных чисел: 1) если в младшем разряде предыдущего значения счётчика имеется 0, то суммирование изменяет лишь цифру младшего разряда на 1; 2) если в m младших разрядах содержится 1, а в (m + 1)—м разряде — 0, то цифры m младших разрядов изменяются на значение 0, а в (m + 1)—м разряде — на значение 1.

Например.

Указанная закономерность используется в счётчиках с параллельным переносом.

При одном и том же числе разрядов предельная частота счётчика с параллельным переносом  $f_{C\Pi}$  будет выше, чем в счётчике последовательного переноса  $f_{\Pi\Pi}$ :

$$f_{\text{C}\Pi\text{max}} \le \frac{1}{\Pi \cdot t_{3M}} \; ; \; f_{\Pi\Pi\text{max}} \le \frac{1}{\Pi \cdot t_{II}} \, ,$$

где  $t_{3N}$  — время срабатывания схемы И;  $t_{\Pi}$  — время переключения триггера;  $\Pi$  — число разрядов счётчика.

Так как  $t_{\Pi} >> t_{3H}$ , то  $f_{\Pi\Pi} << f_{C\Pi}$

При организации декадного счёта применяются последовательнопараллельные схемы переноса (рис. 1.8). Схема такого счётчика состоит из 4 х декад, внутри каждой из которых организуется параллельный перенос, а между декадами — последовательный. С заполнением младшей декады срабатывает схема И и начинает считать 2—я декада, после 16—ти кратного заполнения первой и однократного — второй декады начинает считать третья декада и т. д.

Рис. 1.8. Последовательно-параллельные схемы переноса

Задержка в многоразрядном счётчике будет пропорциональна числу декад. IV. Методические указания.

1. Срисовать с карты У–1 схему счётчика. Для этой схемы заполнить таблицу состояний (табл. 1.3).

Таблица 1.3 Таблица состояний триггеров

| № состояния  |                       | Положения | триггеров |                       |

|--------------|-----------------------|-----------|-----------|-----------------------|

| Н2 СОСТОЯНИЯ | <b>y</b> <sub>4</sub> | У3        | У2        | <b>Y</b> <sub>1</sub> |

| 0            |                       |           |           |                       |

| 1            |                       |           |           |                       |

|              |                       |           |           |                       |

|              |                       |           |           |                       |

|              |                       |           |           |                       |

| П            |                       |           |           |                       |

а). Произвести соединения выходов  $Y \in X$ , чтобы получить модуль счёта  $K_C$ , заданный в таблице 1.4.

#### Модули счета

| Кс                    | 16 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 |

|-----------------------|----|----|----|----|----|----|---|---|---|---|---|---|---|

| <b>X</b> <sub>3</sub> | _  |    |    |    |    |    |   |   |   |   |   |   |   |

| $\chi_2$              | _  |    |    |    |    |    |   |   |   |   |   |   |   |

| <b>X</b> <sub>1</sub> | _  |    |    |    |    |    |   |   |   |   |   |   |   |

|                       |    |    |    |    |    |    |   |   |   |   |   |   |   |

- б). Нарисовать временные диаграммы работы счётчика для  $K_C = 16$ .

- в). Проверить работу счётчика на соответствие таблице 1.4. Для этого наложить карту У—1 на лицевую панель стенда и произвести двоичный счёт входных импульсов, поступающих от формирователя F— $\Gamma$ —, который работает от кнопки SB1.

Коммутацию выходов  $\mathcal{Y}$  с  $\mathcal{X}$  производить специальными одножильными перемычками.

- 2. Дать таблицу состояний триггеров вычитающего 4-разрядного счётчика. Названия строк и столбцов этой таблицы такие же, как в таблице 1.3.

- а). Проверить работу счётчика на соответствие его таблице состояний триггеров. Для этого наложить карту У–2 на лицевую панель и проверить двоичный счёт.

- 3. Срисовать с карты У–3 схему реверсивного счётчика.

- а). Описать работу счётчика и назначение его элементов:

SA1 ÷ SA4 – двоичный код начальной установки счётчика;

SA5 – установка реверса;

SB1 - кнопка для ручной имитации входных импульсов;

SB2 – кнопка разрешения на начальную установку;

SB3 – «Уст. 0»;

HG – индикатор десятичного счёта.

б). Проверить работу реверсивного счётчика в режимах прямого и обратного счёта с предустановкой его начального значения от 0 до 15. Результаты сверить с таблицей 1.5.

#### Предварительная установка реверсивного счетчика

|                                            |   |    |    |    |    | Про | едвар | итель | ная у | стано | вка |    |    |    |    |    |

|--------------------------------------------|---|----|----|----|----|-----|-------|-------|-------|-------|-----|----|----|----|----|----|

|                                            | 0 | 1  | 2  | 3  | 4  | 5   | 6     | 7     | 8     | 9     | 10  | 11 | 10 | 13 | 14 | 15 |

| Число им-<br>пульсов<br>прямого<br>счёта   | 0 | 15 | 14 | 13 | 12 | 11  | 10    | 9     | 8     | 7     | 6   | 5  | 4  | 3  | 2  | 1  |

| Число им-<br>пульсов<br>обратного<br>счёта | 0 | 1  | 2  | 3  | 4  | 5   | 6     | 7     | 8     | 9     | 10  | 11 | 12 | 13 | 14 | 15 |

#### V. Контрольные вопросы.

- 1. Что означает аббревиатура ПЦУ, КЦУ?

- 2. Дать определение для счётчика импульсов.

- 3. Дать классификацию счётчиков импульсов.

- 4. Что не учтено во временной диаграмме рис. 1 в?

- 5. Какой способ переноса осуществляется в схеме счётчика рис. 1 а?

- 6. Что означает модуль счёта?

- 7. Какие триггеры применяются в счётчиках, изображённых на картах У-1 и У-2?

- 8. Нарисуйте схему последовательного счётчика с модулем  $K_C = 10$ .

- 9. В чём суть принудительного насчёта и естественного порядка счёта?

- 10. Видоизменить схему счётчика рис. 3 так, чтобы осуществлялся счёт с  $K_C = 11$ .

- 11. Нарисуйте условное изображение реверсивного счётчика.

- 12. Что такое сквозной перенос?

- 13. Расшифруйте условное изображение счётчика на ИС.

#### **Тема 2** «Исследование арифметико-логического устройства»

I. Цель работы.

Практическое ознакомление с работой арифметико-логического (АЛУ) на ИС.

- II. Задание.

- I. Исследовать работу АЛУ с ручным управлением на ИС типа К155ИП3 с решением задач в машинных кодах.

- III. Теоретическая часть.

<u>Арифметико</u>—логическое устройство предназначено для выполнения арифметических и логических операций над двумя многоразрядными числами. АЛУ является основным устройством ЭВМ. Вместе с устройством управления оно образует <u>процессор</u> (в больших ЭВМ) или <u>микропроцессор</u> (в микро ЭВМ), предназначенный производить кроме арифметических и логических действий и другие <u>микрооперации</u>.

<u>Арифметические операции</u>. АЛУ различных типов способны выполнять разные наборы арифметических операций, например, сложение, вычитание, сдвиг вправо, сдвиг влево. На основе этих арифметических операций можно выполнить и более сложные операции, такие как умножение и деление, приращение положительное, приращение отрицательное.

<u>Логические операции</u>. АЛУ практически любой ЭВМ способны выполнять логические операции И, ИЛИ, Исключающее ИЛИ, НЕ. Рассмотрим, как можно использовать логические операции на примере операции И.

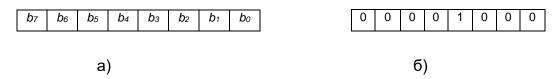

Предположим, что на рис. 2.1 а представлено восьмиразрядное слово информации и необходимо выяснить чему равно содержимое разряда  $b_3 - 0$  или 1.

Рис. 2.1. Восьмиразрядное слово информации:

а) слово; б) маска

Для этого с помощью операции И надо сравнить это число с так называемой маской (рис. 2.1 б). Все биты числа маски равны 0, кроме бита, который должен сравниваться с  $b_3$ ; этот бит равен 1. Для битов от  $b_0$  до  $b_2$  и от  $b_4$  до  $b_7$  результатом сравнения будет 0. Если результат в целом есть 00001000, то  $b_3$  имеет значение 1; если же результат есть 00000000, то  $b_3$  равен 0. Таким образом, единицу из числа можно выделить с помощью маскирования всех других его бит.

Подобные действия имеют практическое применение при маскировании с любым набором битов маски и при использовании других логических операций. В составлении команд языка ассемблера маскирование является мощным средством по реализации логических операций [1].

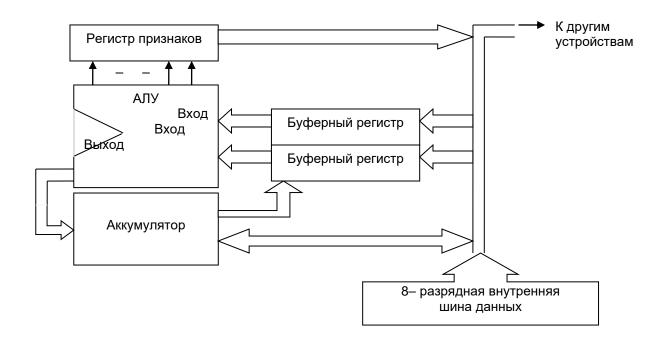

<u>Структурная схема АЛУ</u>. Обычно АЛУ имеет два входных порта, обозначенных как «Вход», и один выходной порт — «Выход» (рис. 2.2).

Рис. 2.2. Структурная схема АЛУ

Оба входных порта снабжены буферами, роль которых выполняют регистры для временного хранения данных (буферные регистры).

Два входных порта позволяют АЛУ принимать данные или с внутренней шины данных, или из специального регистра, именуемого аккумулятором. Последний служит для хранения слова данных, полученного в результате выполнения АЛУ очередной операции.

<u>Регистр признаков</u> предназначен для хранения результатов некоторых проверок, осуществляемых в процессе выполнения логических операций. В случае выполнения определённых условий в отдельные биты регистра признаков будут записаны 1. Таким способом можно кодировать результаты основных операций, выполняемых АЛУ; например, для большинства ЭВМ используются следующие признаки:

- S признак знака, устанавливается, если результат выполнения операции отрицателен;

- Z— признак нуля, устанавливается, если результат выполнения операции равен 0;

- *AC* признак вспомогательного переноса, используется в команде «десятичной коррекции», когда результат суммирования нужно получить в десятичных числах;

- Р признак приоритета, используется при передаче двоичных чисел для

проверок на чётное (или нечётное) количество единиц в слове;

- СУ признак переноса, используется при переполнении разрядной сетки в процессе суммирования. В неиспользованные разряды регистра признаков после «сброса» записываются 0 или 1. Для 8—разрядной микроЭВМ регистр признаков имеет вид как на рис. 2.3.

| S | Z | 0 | AC | С | Р | 1 | СУ |

|---|---|---|----|---|---|---|----|

|---|---|---|----|---|---|---|----|

Рис. 2.3. Регистр признаков

Использование содержимого регистра признаков привело к появлению команд условного перехода. Эти команды предназначены для изменения хода выполнения программы решения задачи на ЭВМ. Более подробную информацию о регистре признаков можно получить в [2].

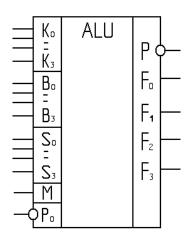

Условное графическое изображение АЛУ (рис. 2.4).

$K_0 - K_3$  — входы первого операнда;

$B_0 - B_3$ — входы второго операнда;

$F_0 - F_3$  — выходы результата операций;

$S_0 - S_3 -$ управляющие входы;

M — признак операции: M = 1 означает первые 32 операции; M = 0 означает вторые 32 операции. В других АЛУ значения этого признака 0 или 1 могут означать соответственно арифметические и логические типы операций;

Рис. 2.4. Условное графическое изображение АЛУ

$P_0$  — вход переноса; P — выход переноса.

В качестве примера в таблице 1 приведены 33 операции; код этих операций определяется сигналами, подаваемыми на управляющие входы S, M и  $P_0$ .

Операции (коды и типы)

Таблица 2.1

#### Код операции Тип операции Примечание «2» M = 0«16» M = 1S<sub>3</sub> S<sub>2</sub> S<sub>1</sub> S<sub>0</sub> 3 4 1 При *P* = 1 $A^{-}$ 0 0 0 0 0 $\boldsymbol{A}$ 0 0 0 1 $A \vee B$ $\overline{A \vee B}$ 2 0 0 1 0 $A \wedge B$ $A \vee B$ 3 0 0 1 1 0 0 0 0 1 1 1 1 При $P_0 = 1$

| 4 | 0 1 0 0 | $\overline{A \wedge B}$ | $A + A \wedge \overline{B}$        | «                         |

|---|---------|-------------------------|------------------------------------|---------------------------|

| 5 | 0 1 0 1 | $\overline{B}$          | $A \lor B + A \land B$             | «                         |

| 6 | 0 1 1 0 | $A \oplus B$            | $A + \overline{B}$                 | $A - B$ При $P_0 = 0$ ; М |

| 7 | 0 1 1 1 | $A \wedge \overline{B}$ | $A \wedge B - 1$                   | При $P_0 = 1$             |

| 8 | 1 0 0 0 | $\overline{A} \vee B$   | $A + A \wedge B$                   | «                         |

| 9 | 1 0 0 1 | $\overline{A \oplus B}$ | A + B                              | «                         |

| А | 1 0 1 0 | В                       | $A \vee \overline{B} + A \wedge B$ | «                         |

| В | 1 0 1 1 | $A \wedge B$            | $A \wedge B + 1$                   | «                         |

| С | 1 1 0 0 | 1 1 1 1                 | A + A                              | «                         |

| D | 1 1 0 1 | $A \vee B$              | $A \vee B + A$                     | «                         |

| Е | 1 1 1 0 | $A \vee B$              | $A \vee \overline{B} + A$          | «                         |

| F | 1 1 1 1 | A                       | A-1                                | «                         |

Продолжить эту таблицу для остальных команд (всего 64 команды) можно, задав  $P_0 = 0$ .

Наличие входа переноса Р0 и выхода переноса Р даёт возможность наращивать разрядность АЛУ. Наращивание осуществляют с помощью дополнительной микросхемы СУП (схема ускоренного переноса). Так, СУП 564ИП4 позволяет объединить четыре АЛУ 564ИП3 и получить 16—разрядное АЛУ.

На основе микросхемы АЛУ, СУП и других можно строить различные вычислительные устройства автоматики, управляемые системой команд, т. е. работающие под управлением программ. АЛУ входит в структуры микропроцессорных систем.

#### IV. Методические указания к карте У1-1.

Для лучшего понимания работы АЛУ в установке используется ручное управление. 16—ричный код операндов набирается кнопкой *SB1* с контролем по индикатору *HG*1. Двоичный код адресата нужного устройства набирается переключателями *SA3*, *SA2*, *SA1*; кнопкой *SB3* производится разрешение про-

хождения кода адреса с выхода счётчика в нужное устройство. В таблице 2.2 даны коды этих устройств.

Таблица 2.2 Коды устройств

| Двоичный код адреса | Нешение уствейства                            |  |  |  |  |

|---------------------|-----------------------------------------------|--|--|--|--|

| SA3 SA2 SA1         | Наименование устройства                       |  |  |  |  |

| 0 0 0               | К – регистр 1-го операнда;                    |  |  |  |  |

| 0 0 1               | В — регистр 2-го операнда;                    |  |  |  |  |

| 0 1 0               | S — регистр кода операции;                    |  |  |  |  |

| 1 0 0               | R — вход считывания с аккумулятора;           |  |  |  |  |

| 1 0 1               | У — разрешающий вход на запись в аккумулятор. |  |  |  |  |

#### Примеры решения задач по составлению программ в кодах машины.

Задача 1. Дано  $A = 5_{16}$ ,  $B_{16} = 3_{16}$ ; из A вычесть B, результат инвертировать. Ответ:  $\mathcal{L}_{16}$ .

#### Решение проведём по шагам:

- 1. Ввести код операции «6» (при M = 0,  $P_0 = 0$  см. табл. 2.1), нажимая на кнопку SB1 нужное число раз. Контроль за введённым числом производить по дисплею HG1.

- 2. Набрать переключателями SA3, SA2, SA1 адрес 010, соответствующий регистру кода операции (см. табл. 2).

- 3. Нажав на кнопку *SB*3, переслать введённый код в регистр *S*. Контроль производить по свечению светодиода *HL*3.

- 4. Ввести операнд  $K = 5_{16}$ . Контроль по HG1.

- 5. Набрать адрес регистра операнда K (SA3, SA2, SA1 = 000) и, нажав на кнопку SB3, переписать введённое значение операнда K в регистр K. Контроль по свечению HL1.

- 6. Ввести операнд  $B = 3_{16}$  с помощью кнопки SB1. Контроль по HG1.

- 7. Набрать адрес регистра операнда B(SA3, SA2, SA1 = 001) и с помощью кнопки SB3 переписать введённое значение в регистр B. Контроль по HL2.

- 8. Набрать адрес аккумулятора (SA3, SA2, SA1 = 101) и, нажав на кнопку SB3, переписать результат выполнения операции (S, M,  $P_0$ ) над введёнными

операндами ( $K = 5_{16}$ ,  $B = 3_{16}$ ) с выхода АЛУ в аккумулятор. Контроль за операцией перезаписи по свечению HL5. Результат операции считывается в виде 16—ричного кода с дисплея HG1 и сигнала переноса в старший разряд (только при выполнении арифметических задач) с индикатора HL6.

- 9. Набрать адрес операнда регистра K (SA3, SA2, SA1 = 000), переписать число из аккумулятора в регистр K результат (A-B). При этом нажать на кнопку SB3 и контролировать по HL1.

- 10. Набрать код операции «0» кнопкой SB1 (при этом M = 0,  $P_0 = 1$ ) и ввести его в регистр S (SA3, SA2, SA1 = 010) нажатием кнопки SB3.

Примечание. Код операции «0» можно также получить, сбросив счётчик в 0. Для этого набрать SA3, SA2, SA1 =  $100_2$  и нажать на кнопку SB3. Контроль по *HL4*.

11. Набрать адрес аккумулятора (SA3, SA2, SA1 = 101) и, нажав на кнопку SB3, переписать результат с выхода АЛУ в аккумулятор.

Задача 2. Вычесть из числа  $A = 3_{16}$  число  $B = 5_{16}$ . Ответ будет  $E_{16}$ .

Проверьте ответ, решив эту задачу вручную, представляя отрицательное число дополнительным кодом.

#### Решение.

1. По команде 01102 = «6» происходит сложение числа A и B, причём первое слагаемое представлено в прямом, а второе слагаемое B - B дополнительном двоичных кодах. Поскольку по абсолютной величине B > A, то разность будет в дополнительном коде:

Если бы выполнялось условие |B| < |A|, то разность была бы в прямом двоичном коде. Таким образом, признаком отрицательного числа служит 1 в старшем разряде двоичного числа.

Задача 3. Вычесть из числа  $A = 3_{16}$  число  $B = 3_{16}$ . Ответ должен быть 0. Ручная проверка с представлением вычитаемого в дополнительном коде даст тот же результат:

Единица результата «теряется», выходя за пределы разрядной сетки.

Признаки нулевого, отрицательного и положительного результатов, как говорилось в разделе III, фиксируются соответствующими битами регистра признаков (этот регистр в лабораторном стенде отсутствует).

Задача 4. Сложить число  $A = 9_{16}$  с числом  $B = A_{16}$ . Индикатор HG1 высветит цифру 3, при этом нужно учитывать в качестве старшего разряда результата единицу переноса, о чём свидетельствует P = 1 светодиод HL6. Следовательно, окончательный ответ будет  $13_{16}$ .

Примечание. Сигнал переноса нужно учитывать только при выполнении арифметических операций суммирования.

#### V. Контрольные вопросы.

- 1. Чем отличается микропроцессор от процессора?

- 2. Перечислите основные арифметические и логические операции, выполняемые АЛУ.

- 3. Для чего служит регистр признаков?

- 4. Какую роль выполняет аккумулятор?

- 5. Дать условное графическое изображение АЛУ.

- 6. Какие признаки должен бы иметь регистр признаков изучаемого АЛУ?

### **Тема 3 «Исследование оперативной памяти и мультиплексной организации шины данных»**

#### І. Цель и содержание.

Практическое ознакомление с принципами работы оперативного запоминающего устройства (ОЗУ) и исследованием мультиплексного способа организации внутренней шины данных.

- II. Задание.

- 1. Исследовать работу ОЗУ в режимах записи и считывания.

- 2. Исследовать мультиплексный способ организации внутренней шины данных.

#### III. Теоретическая часть.

Микросхемы памяти широко применяются в современной электронной аппаратуре самого различного назначения. Мы ознакомились, в частности, с ПЗУ (постоянное запоминающее устройство), которое использовалось совместно с дешифратором для преобразования кодов в устройстве отображения информации [2]. Основное же назначение памяти — это использование её в современных ЭВМ. Как функциональная часть ЭВМ память служит для записи, хранения и выдачи команд и обрабатываемых данных.

Комплекс технических средств, реализующих функцию памяти, называется запоминающим устройством (ЗУ).

Мы изучали арифметико-логическое устройство с ручным управлением. С автоматическим управлением это устройство называется микропроцессором. Для обеспечения работы микропроцессора необходима программа, т. е. последовательность команд, и данные, над которыми процессор производит предписываемые командами операции. Команды и данные поступают в ос-

новную память ЭВМ через устройство ввода, на выходе которого они получают цифровую форму представления,

т. е. форму кодовых комбинаций 0 и 1.

Основная память, как правило, состоит из ЗУ двух типов — оперативного (ОЗУ) и постоянного (ПЗУ).

ОЗУ предназначено для хранения переменной информации и допускает изменение своего содержимого в ходе выполнения микропроцессором вычислительных операций с данными. Это значит, что микропроцессор может выбрать из ОЗУ код команды и данные после обработки поместить в ОЗУ новые данные на места прежних, которые в этом случае перестают существовать. Таким образом, ОЗУ может работать в режимах записи, считывания и хранения информации.

ПЗУ содержит информацию, которая не должна изменяться в ходе выполнения микропроцессором программы. Такую информацию составляют стандартные программы, табличные данные, коды физических констант и постоянных коэффициентов и т. д. Эта информация заносится предварительно, например, путём электрического сигнала, и в ходе работы микропроцессора может только считываться. ПЗУ, таким образом, целесообразно прежде всего использовать в специализированных автоматических устройствах, работающих по постоянной программе.

Микросхемы памяти изготавливают по полупроводниковой технологии на основе кремния с высокой степенью интеграции элементов и компонентов на кристалле, что определяет их принадлежность к большим интегральным схемам (БИС). Конструктивно БИС памяти представляет собой полупроводниковый кристалл с площадью в несколько десятков квадратных миллиметров, заключённый в корпус.

Общие характеристики БИС памяти: информационная ёмкость [бит или байт], быстродействие [нс], энергопотребление [Вт].

Основной составной частью микросхем ОЗУ и ПЗУ является массив элементов памяти (ЭП), объединённых в матрицу накопителя.

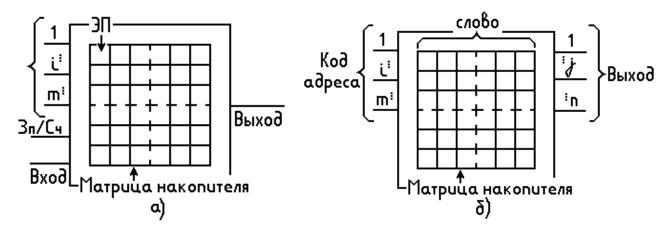

Элемент памяти может хранить один бит (0 или 1) информации. Каждый ЭП имеет свой адрес. Такая организация ОЗУ называется одноразрядной (рис. 3.1 а).

Рис. 3.1. **Организация ОЗУ:** а – одноразрядная; б - многоразрядная

При обращении к ЭП, последний выбирается с помощью кода адреса, сигналы которого подводятся к соответствующим выводам микросхемы.

Запоминающее устройство (ОЗУ или ПЗУ), которое допускает обращение по адресу к любому ЭП в произвольном порядке, называется <u>запоминающим</u> устройством с произвольной выборкой (ЗУПВ).

Число двоичных разрядов кода адреса должно быть такое, чтобы имелась возможность адресоваться к любому ЭП. Например, в микросхеме ОЗУ, содержащей 1024 ЭП, число адресных разрядов должно быть m = 10, т. к.  $2^{10} = 1024$ . (Заметим, что для обозначения числа  $2^{10} = 1024$  в вычислительной технике применяют букву K).

Для ввода и вывода информации служит вход и выход микросхемы. Для управления режимом (записи или считывания) служит сигнал «запись—считывание» (*W/R*). Если этот сигнал равен 1, то происходит запись, если 0 — считывание.

Некоторые ОЗУ и все ПЗУ имеют многоразрядную организацию, инаце называемую «словарной» (рис. 3.1 б). У таких микросхем насколько информационных входов и столько же выходов, и поэтому они допускают одно-

временную запись (считывание) многоразрядного кода, который принято называть «словом» или ячейкой памяти.

Для построения ОЗУ на микросхемах с одноразрядной организацией необходимо объединить микросхемы с тем, чтобы обеспечить возможность записи информации в ОЗУ, её хранение и считывание в форме многоразрядного цифрового кода, т. е. слова.

Микросхемы ОЗУ по типу ЭП разделяют на статические и динамические. В статических ОЗУ в качестве ЭП применены статические триггеры. Число состояний, в которых может находиться триггер, равно двум, что и позволяет использовать его для хранения двоичной единицы информации (бит).

В микросхемах динамических ОЗУ элементы памяти выполнены на основе электрических конденсаторов, сформированных внутри полупроводникового кристалла. Такие ЭП не могут долгое время сохранять своё состояние, определяемое наличием или отсутствием электрического заряда, и поэтому нуждаются в периодическом восстановлении (регенерации). Динамические ОЗУ сложнее в применении, поскольку нуждаются в организации принудительной регенерации, в дополнительном оборудовании и в усложнении устройств управления.

В микросхемах ПЗУ функции ЭП выполняют перемычки в виде проводников, диодов, транзисторов между шинами строк и столбцов в накопителе. В такой матрице наличие перемычки соответствует, например, 1, а её отсутствие — 0.

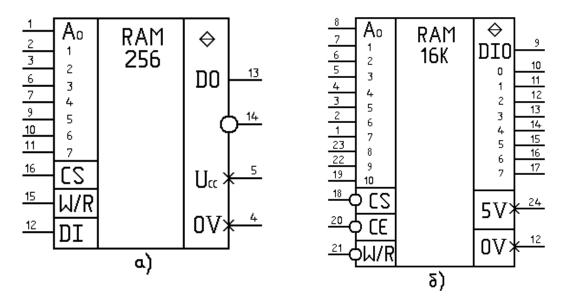

Микросхема памяти как функциональный узел. На рис.3.2 приведены условные графические изображения статических одноразрядного (рис. 3.2 а) и со словарной организацией (рис. 2.2 б) ОЗУ. Первое предназначено для хранения — 256x1 бит, а второе — 2048x8 = 16 кбайт.

Рис. 3.2. Условные графические изображения статических одноразрядного (а) и со словарной организацией (б) ОЗУ

Сигналы и соответствующие выводы микросхем можно подразделить на адресные, управляющие и информационные. Отдельную группу составляют выводы для подключения напряжения источника питания. Ниже приведены обозначения сигналов и выводов в соответствии с ГОСТ 1948–74:

$A_0 \div A_{10}$  — адресные входы,

CS — выбор микросхемы,

ОЕ— разрешение по выходу (используется при считывании),

*W/R*— запись-считывание,

**Д1** — входные данные,

D0 — выходные данные,

**Д10** — данные: вход-выход,

$U_{CC}$  — напряжение питания,

ОУ — общий вывод микросхемы.

На рис. 3.2а представлено условное изображение микросхемы статического ОЗУ типа К561РУ2. Число адресных входов позволяет определять информационную ёмкость микросхемы: 2<sup>8</sup> = 256 бит. Наличие одного информационного входа Д1 и одного выхода Д0 (прямого и инверсного) указывает на одноразрядную организацию микросхемы памяти: 256х1 бит.

Для управления режимом работы предусмотрены два сигнала:  $\overline{CS}$  (выбор микросхемы) и *W/R* (запись—считывание). Сигнал  $\overline{CS}$  разрешает или запрещает обращение к микросхеме по информационным входу и выходу. Наличие на этом входе сигнала с уровнем логической 1 однозначно определяет режим хранения. При этом выход принимает высокоомное состояние, при котором он электрически отключён от приёмника информации. Имея в виду, что обычно у микросхемы выход может находиться в одном из двух состояний, соответствующих логическим 0 и 1, указанное высокоомное (иначе — высокоимпедансное) состояние называется третьим. Выходное напряжение в третьем состоянии имеет уровень, равный приблизительно половине наибольшего значения выходного напряжения. Наличие у микросхемы выхода на три состояния указывается на правом поле её условного изображения специальным знаком:

- $\diamondsuit$  выход на три состояния,

- $igoplus_{-}$  выход с открытым эмиттером ОЭ  $\emph{n-p-n}$  транзистора,

$\bigcirc$  — выход с открытым коллектором ОК n–p–n транзистора, с открытым стоком ОС (МДП–транзистора с n–каналом). При обращении к микросхеме через вход  $\mathcal{L}1$  для записи или считывания одного бита информации необходимо подать разрешающий сигнал  $\overline{CS}$  и сигнал W/R с уровнем: при записи — 1, при считывании — 0. Вход и выход микросхемы К561РУ2 развязаны, т. е. на могут влиять на состояния друг друга. Таким свойством обладают микросхемы с выходами на три состояния. Учитывая отмеченную особенность, можно объединять входы и выходы микросхемы и подключить их к общей информационной шине, по которой информация подаётся к микросхеме и выводится из неё.

На рис. 3.26 приведено условное изображение статического ОЗУ типа КР573РУ8 со словарной организацией, позволяющее производить запись и считывание информации 8–разрядными словами (байтами). Причём входы и выходы совмещены и обладают свойством двунаправленной проводимости. Сигнал  $\overline{OE}$  разрешает выход, т. е. разрешает считывание при  $\overline{CS}=0$  .

Таблицы истинности для микросхем рис. 1 приведены соответственно в таблицах 3.1 и 3. 2.

Таблица истинности

Таблица истинности

| $\overline{CS}$ | W/R | A₀ ÷ A₁₀ | Д1 | Д0                          | Режим работы |

|-----------------|-----|----------|----|-----------------------------|--------------|

| 1               | X   | X        | X  | Z                           | Хранение     |

| 0               | 1   | Α        | 0  | Z                           | Запись 0     |

| 0               | 1   | Α        | 0  | Z                           | Запись 1     |

| 0               | 0   | Α        | X  | д, $\overline{\mathcal{A}}$ | Считывание   |

Примечание. X — произвольное состояние (0 или 1); Z — высокоомное.

Таблица истинности

Таблица 3.2

| $\overline{CS}$ | $\overline{OE}$ | W/R | $A_0 \div A_{10}$ | <b>д10</b> <sub>0</sub> ÷ Д10 <sub>7</sub> | Режим работы      |

|-----------------|-----------------|-----|-------------------|--------------------------------------------|-------------------|

| 1               | X               | Χ   | X                 | Z                                          | Хранение          |

| 0               | X               | 0   | Α                 | 0                                          | Запись 0          |

| 0               | X               | 0   | Α                 | 1                                          | Запись 1          |

| 0               | 1               | 1   | Α                 | Z                                          | Чтение без выдачи |

| 0               | 0               | 1   | Α                 | До ÷Д7                                     | Считывание        |

#### IV. Методические указания.

На карте У1–3 изображена схема ОЗУ с ручным управлением. По индивидуальному заданию преподавателя произвести запись и считывание информации. Двоичный код адреса нужного устройства набирается переключателями SA3, SA2, SA1; кнопкой SB3 производится выбор устройства в соответствии с набранным адресом (см. таблицу 3.3).

Таблица 3.3

#### Устройства с кодами адресов

| <b>Двоичный код адреса</b><br>SA3 SA2 SA1 | Наименование устройства                                                             |

|-------------------------------------------|-------------------------------------------------------------------------------------|

| 0 1 1                                     | C = 1 – параллельный регистр адреса ячейки ОЗУ;<br>контроль по <i>HL2</i> «запись». |

| 0 | W = 1 — выбор микросхемы ОЗУ;    |

|---|----------------------------------|

|   | контроль по <i>HL3</i> «чтение». |

Шестнадцатеричный код операндов (код адреса ячейки памяти или данные) набирается кнопкой SB1 с контролем по блоку индикации (БИ). В зависимости от сигнала на входе A мультиплексор  $\mathcal{L}2$  передаёт на внутреннюю шину данные счётчика  $\mathcal{L}10$  (A = 0, кнопка SB2 отжата), либо содержимое выбранной ячейки O3Y (A = 1, кнопка SB2 нажата).

#### Примеры решения типовых задач.

Задача 1. Обнулить содержимое нулевой ячейки ОЗУ.

1

#### Решение.

- 1. Нажимая на кнопку *SB1* добиться, чтобы индикатор БИ показал число 0<sub>16</sub>.

- 2. Переключателями  $SA1 \div SA3$  набрать код адреса регистра  $RG A 011_2$  (SA3 старший разряд).

- 3. Нажатием кнопки *SB3* набираем нулевой адрес ячейки O3У; контроль по *HL*2.

- 4. Переключателями  $SA1 \div SA3$  набрать код адреса самого устройства ОЗУ  $-110_2$ .

- 5. Нажатием кнопки *SB*3 в ячейку ОЗУ по нулевому адресу запишется число  $0000_2$  по входам  $\mathcal{L}1 \div \mathcal{L}8$  ОЗУ. Контроль по *HL*3.

#### Задача 2. Прочитать содержимое нулевой ячейки ОЗУ.

#### Решение.

- 1. Нажимая на кнопку SB1 набрать адрес ячейки; контроль по БИ.

- 2. Переключателями SA1  $\div$  SA3 набрать код адреса регистра RG–A 011<sub>2</sub>.

- 3. Нажатием кнопки SB3 зафиксировать набранный адрес на адресной шине O3У ( $A1 \div A8$ ).

- 4. Нажатием кнопки *SB2* произвести считывание нулевой ячейки ОЗУ. Контроль по БИ.

#### V. Контрольные вопросы.

- 1. Что называют запоминающим устройством?

- 2. Что относят к понятию «микропроцессор»?

- 3. Какую роль исполняют ОЗУ, ПЗУ?

- 4. Какими параметрами можно оценить работу памяти ЭВМ?

- 5. Что является элементом памяти ОЗУ современных ЭВМ?

- 6. Чем отличается многоразрядная организация ОЗУ от одноразрядной?

- 7. Каково назначение выводов различных микросхем ОЗУ?

#### Тема 4 «Исследование модели четырехразрядного микропроцессора»

I. Цель и содержание.

Практическое ознакомление с архитектурой и принципами функционирования микропроцессора на примере четырехразрядной модели. Освоение выполнения команд в ручном режиме.

- II. Задание индивидуальное каждому студенту:

- 1. Изучить структуру и логику работы четырехразрядной микроЭВМ (микропроцессора).

- 2. Разработать алгоритм (программу) на машинных кодах для выполнения индивидуального задания.

- III. Теоретические сведения.

Приступая к изучению микроЭВМ мы предварительно ознакомились с её основными устройствами: АЛУ и ОЗУ. Кроме этих устройств, к основным следует отнести устройство управления (УУ), которое чрезвычайно важно в поддержании требуемой последовательности включения и выключения АЛУ, ОЗУ и всех остальных устройств (регистров, счётчиков, внешних устройств).

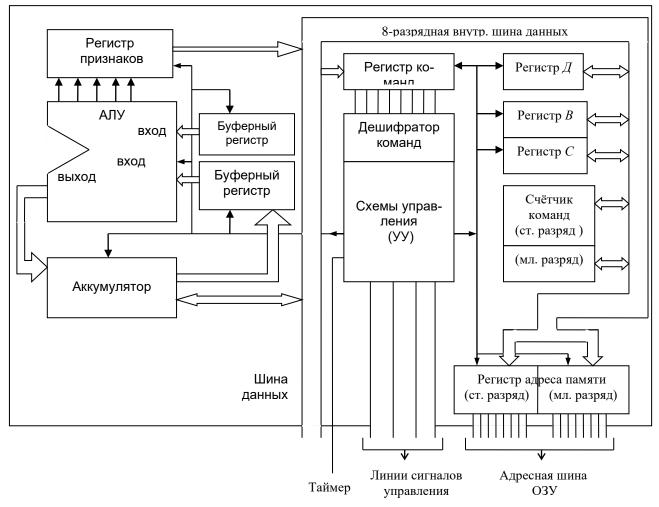

На рис. 1 приведена структурная схема 8—разрядной микроЭВМ, в которой сигналы управления поступают от УУ (по одиночному проводу) на все внутренние и внешние звенья типичной малоразрядной микроЭВМ.

Рис. 4.1. Структурная схема 8-разрядной микроЭВМ

Устройство управления начинает работать с момента пуска машины. В счётчик команд записывается адрес первой команды программы, хранящейся в ОЗУ. Этот адрес затем посылается из счётчика команд в регистр адреса памяти. Считывается содержимое ячейки с указанным адресом. Этим содержимым должен быть код команды (но не данные). Из ОЗУ код команды по шине данных пересылается в регистр команд. С выходов регистра команд код параллельно поступает на дешифратор команд и декодируется им. В соответствии с кодом команды с УУ, поступают последовательно управляющие сигналы на все звенья микроЭВМ.

Обмен информацией между устройствами производится в двух направлениях. Это становится возможным для микромодулей с тремя состояниями по отношению к шине данных: приёма, передачи и отключения, т. е. мультиплексная организация шины данных. С извлечением кода команды из ОЗУ,

даётся приращение +1 содержимому счётчика команд. Это приращение счётчик получает как раз в тот момент, когда начинает выполняться команда, только что извлечённая из ОЗУ. Следовательно, начиная с этого момента, счётчик команд «указывает», какой будет следующая команда. Так будет продолжаться до извлечения из ОЗУ последней команды программы. Нормальный ход программы может быть нарушен, если в счётчик команд записать другой адрес, выпадающий из последовательности команд основной программы. Такое «нарушение» происходит с помощью команд перехода (условного и безусловного), которыми пользуются для вызова подпрограмм (подпрограмма — часть программы, оформленная в виде, допускающем многократное обращение к ней из различных точек основной программы). По выполнении подпрограммы нормальная последовательность команд основной программы восстанавливается с помощью команды возврата.

Регистры общего назначения (регистры В, С, Д) служат для временного хранения информации в процессе выполнения текущей команды. Обычно операции, использующие эти регистры, влияют на содержимое регистра признаков.

По четырём линиям управления поступают сигналы на дешифраторы адресов устройств ввода-вывода (две линии) и накопителей ОЗУ (две линии). Таким образом, одновременное разрешение на включение (инициализацию) возможно одному из четырёх устройств ввода-вывода или одному из четырёх накопителей ОЗУ.

По линии «таймер» на УУ поступают тактовые сигналы, синхронизирующие во времени работу всей микроЭВМ.

#### IV. Методические указания.

На карте 1У—2 изображена схема четырёхразрядной микроЭВМ с ручным управлением. Роль УУ при работе такой машины будет выполнять студент. Поэтому в схеме отсутствуют само УУ, дешифраторы адресов устройств ввода-вывода и накопителей ОЗУ.

В состав исследуемой микроЭВМ входят:

- дешифратор адреса устройств машины (дешифратор Д1);

- переключатели *SA4*, *SA5* и кнопки *SB1*  $\div$  *SB3* для формирования сигналов управления;

- микропроцессор, состоящий из АЛУ (Д9), аккумулятора (Д10), регистра команд S (Д7) и буферных регистров *К*, *B* (Д5, Д6);

- оперативное запоминающее устройство (Д4) с регистром адресов А (Д8);

- внутренняя шина данных с мультиплексным управлением от мультиплексора группового управления Д2 (при A=0 на шину данных коммутируются входы X, при A=1 входы Y);

- блок индикации, включающий ПЗУ с дешифратором на ДЗ для семисегментного индикатора *HG1*.

В буферных регистрах *К* и *В* хранится содержимое операндов *А* и *В* соответственно при выполнении команд, требующих обращений к АЛУ. Двоичный код адреса нужного устройства набирается вручную переключателями *SA3*, *SA2*, *SA1* (*SA3* — старший разряд). Данные имитирует содержимое счётчика (Д10). При опросе по входу «У» счётчик работает в качестве аккумулятора, фиксируя результат выполнения очередной операции, производимой АЛУ. Кнопкой SB1 производится приращение содержимого счётчика на +1. Кнопкой SB3 осуществляется инициализация одного из устройств машины в зависимости от кодовой комбинации, набранной переключателями. В таблице 3.1 даны коды адресов устройств машины. Кнопкой *SB2* на шину данных можно вывести содержимое ячеек ОЗУ при их опросе через регистр адреса *A*.

Таблица 3.1 Коды команд устройств с адресами

| Двоичный код адреса | <b>Чаимонорацию устройства</b>        |  |  |

|---------------------|---------------------------------------|--|--|

| SA3 SA2 SA1         | Наименование устройства               |  |  |

| 0 0 0               | <i>К</i> —регистр первого операнда;   |  |  |

| 0 0 1               | <i>B</i> — регистр второго операнда;  |  |  |

| 0 1 0               | S — регистр кода операции;            |  |  |

| 0 1 1               | A — регистр адреса ячейки ОЗУ;        |  |  |

| 1 0 0               | R — сброс в «0» содержимого счётчика; |  |  |

| 1 | 0 | 1 | У — разрешающий вход на запись в аккумулятор;                        |

|---|---|---|----------------------------------------------------------------------|

|   |   |   | $\overline{\overline{W}}$ — разрешение на запись в ОЗУ;              |

| 1 | 1 | 0 | W— разрешение на считывание с ОЗУ (контроль по <i>HG1</i> с нажатием |

|   |   |   | кнопки <i>SB</i> 2).                                                 |

В таблице 3.1 приведены коды некоторых команд, выполняемых изучаемой микроЭВМ.

Пример решения типовой задачи по разработке алгоритма с использованием машинных кодов.

Задача 1. Операнду А присвоить значение  $0000_2$  и записать это число в аккумулятор, скопировать это число с аккумулятора в нулевую ячейку ОЗУ; содержимое аккумулятора ещё раз скопировать, но уже в регистр K, инвертировать это число и поместить в аккумулятор, затем в первую ячейку ОЗУ.

#### Решение.

Решение проведём по шагам.

- 1. Нажимая на кнопку *SB1* нужное число раз, ввести код операции «3<sub>16</sub>» (при M = 1,  $P_0 = 1$  см. таблицу 1 лабораторной работы №7), означающей «присвоить значение «0000<sub>2</sub>» операнду, хранящемуся в регистре K». Контроль производить по  $HG1 = 3_{16}$ .

- 2. Набрать переключателями 0102 код адреса регистра S (см. таблицу 1);

- 3. С нажатием кнопки *SB3* произойдёт присвоение нулевого значения операнду, хранящемуся в регистре K, т. е. K = 0. Контроль по HL4.

- 4. Переслать информацию из АЛУ в аккумулятор; для этого переключателями набрать адрес аккумулятора 101<sub>2</sub> (см. табл. 3.1).

- 5. Нажав на кнопку *SB*3, переслать информацию из АЛУ в аккумулятор. Контроль по *HL*7 и  $HG = 0_{16}$ .

- 6. Кнопкой SB1 набрать адрес нулевой ячейки. Контроль  $HG = 0_{16}$ .

- 7. Набрать переключателями SA3, SA2, SA1 0112 код адреса регистра A.

- 8. Нажатием кнопки *SB3* адрес нулевой ячейки будет зафиксирован в регистре А. Контроль по *HL5*.

- 9. Содержимое аккумулятора переслать в нулевую ячейку ОЗУ. Для этого переключателями набрать код 110<sub>2</sub>, означающий адрес ОЗУ.

- 10. Нажатием кнопки *SB3* содержимое аккумулятора скопируется в нулевую ячейку. Контроль по *HL8*.

- 11. Содержимое аккумулятора поместить в регистр K. Для этого переключателями набрать  $0000_2$  код адреса регистра K.

- 12. С нажатием кнопки *SB3* содержимое аккумулятора скопируется в регистр К. Контроль по *HL2*.

- 13. Инвертировать число, содержащееся в регистре K. Для этого ввести код « $O_{16}$ » (при M=1,  $P_0=1$ ), нажимая на кнопку SB1. Контроль по HG1=0.

- 14. Набрать переключателями 010<sub>2</sub> код адреса регистра S АЛУ.

- 15. С нажатием кнопки *SB3* АЛУ произведёт инвертирование содержимого регистра *К*. Контроль по *HL4*.

- 16. Кнопкой *SB*1 набрать «1<sub>16</sub>» код адреса ячейки ОЗУ. Контроль по *HG* = 1<sub>16</sub>.

- 17. Переключателями 0112 код набрать код адреса регистра А.

- 18. Нажатием на кнопку *SB3* выбирается адрес первой ячейки ОЗУ. Контроль по *HL5*.

- 19. Переключателями набрать 1012 код адреса аккумулятора.

- 20. С нажатием кнопки *SB3* в аккумулятор будет занесено содержимое АЛУ после операции инвертирования. Контроль по  $HG1 = F_{16}$  и HL7.

- 21. Переключателями набрать 1102 код адреса ОЗУ.

- 22. С нажатием кнопки *SB3* произойдёт запись содержимого аккумулятора в первую ячейку ОЗУ.

#### Проверка.

Проверку правильности составления алгоритма можно произвести путём считывания содержимого ячеек 0 и 1. Например, чтобы прочесть содержимое первой ячейки нужно кнопкой SB1 по индикатору *HG1* получить число «1<sub>16</sub>», переключателями набрать 011<sub>2</sub> код адреса регистра А. Кнопкой *SB3* зафиксировать адрес первой ячейки в регистре А. Затем набрать 110<sub>2</sub> код адреса

накопителя ОЗУ; кнопкой *SB3* зафиксировать этот код в регистре *A* и, нажав на кнопку *SB2*, считать содержимое первой ячейки.

Ответ: в нулевой ячейке записано число 016, в первой ячейке —  $F_{16}$ .

#### V. Контрольные вопросы.

- 1. Какие функции выполняются устройствами АЛУ, ПЗУ, ОЗУ, УУ?

- 2. Какую функцию выполняет устройство на ИС Д2 схемы карты У1—2?

- 3. Какие функциональные признаки принадлежат регистрам общего назначения, отличающие их от регистров буферных?

- 4. Перечислите различные признаки между микроЭВМ изображённой на схеме карты 1У—2 и схемы рис. 3.1.

- 5. Какие звенья входят в УУ?

- 6. Какую роль выполняют: счётчик команд, дешифратор команд, сигналы управления, шина данных?

#### БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- 1. Новикова, Н. В. Электрические и электронные компоненты устройств и систем. Лабораторный практикум : учебное пособие / Н. В. Новикова, В. О. Афонько. Минск : РИПО, 2022. 187 с. ISBN 978-985-895-043-9. Текст : электронный // Лань : электронно-библиотечная система. URL: https://e.lanbook.com/book/334229.

- 2. Электрические и электронные компоненты устройств и систем. Лабораторный практикум: учебное пособие / В. В. Хорошко, С. М. Боровиков, А. А. Фещенко, Я. А. Соловьёв. БГУИР: БГУИР, 2023. 80 с. ISBN 978-985-543-672-1. Текст: электронный // Лань: электронно-библиотечная система. URL: https://e.lanbook.com/book/479468

#### Учебное издание

#### Составители:

# Судник Юрий Александрович Четвериков Евгений Александрович Шабаев Евгений Адимович Беленов Виталий Николаевич

## «Электронные компоненты микропроцессорных устройств»

Методические указания

Издано в редакции составителей Корректура составителей Отпечатано с оригинала, предоставленного составителями

Подписано в печать .2025 г. Формат  $60x84\ 1/16$  Усл. печ. л. . Уч.-изд. л. . Изд. № . Зак. .